作者:原创

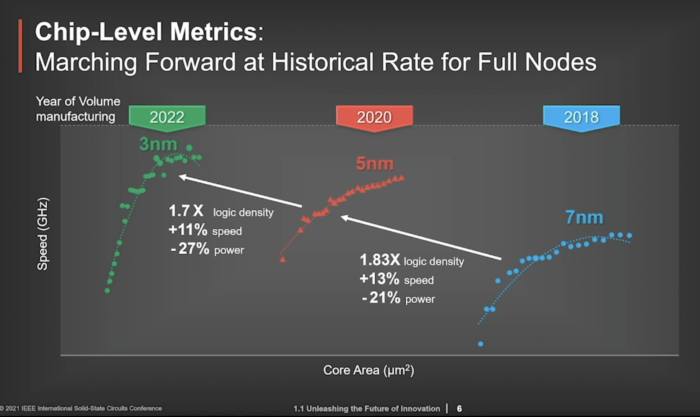

台积电董事长刘德音(Dr. Mark Liu)证实,该公司的下一代 3nm 芯片制造节点,正在按计划推进之中。与 5nm 制程节点相比,3nm 可提供几乎翻番的逻辑密度,辅以 11% 的性能提升、或 27% 的能效改进;预期明年有望转入试生产。

台积电高管在早前的国际固态电路会议(ISSCC)演讲期间的这番表态,证实了该公司对下一代制造技术的信心。在满足当前和未来产品的日益增长需求的同时,即便汽车领域的产品需求有所提升,也不会对整体产能造成太大影响。

需要指出的是,部分媒体误解了所谓的“3nm 工艺提前”。毕竟在主题为《释放创新未来》的 27 分钟演讲期间,高管并未直言此事,仅在开头和结尾对 3nm 开发进度“顺口一提”。

除了透露 3nm 技术的发展正在如期推进且相当顺利,刘德音还提供了对 3nm 工艺的最新数据、以及对工艺发展的看法。他指出,到目前为止,台积电已出货约 18 亿片基于 7nm 工艺节点的芯片。截止 2020 年,该公司一直是行业中的领跑者。

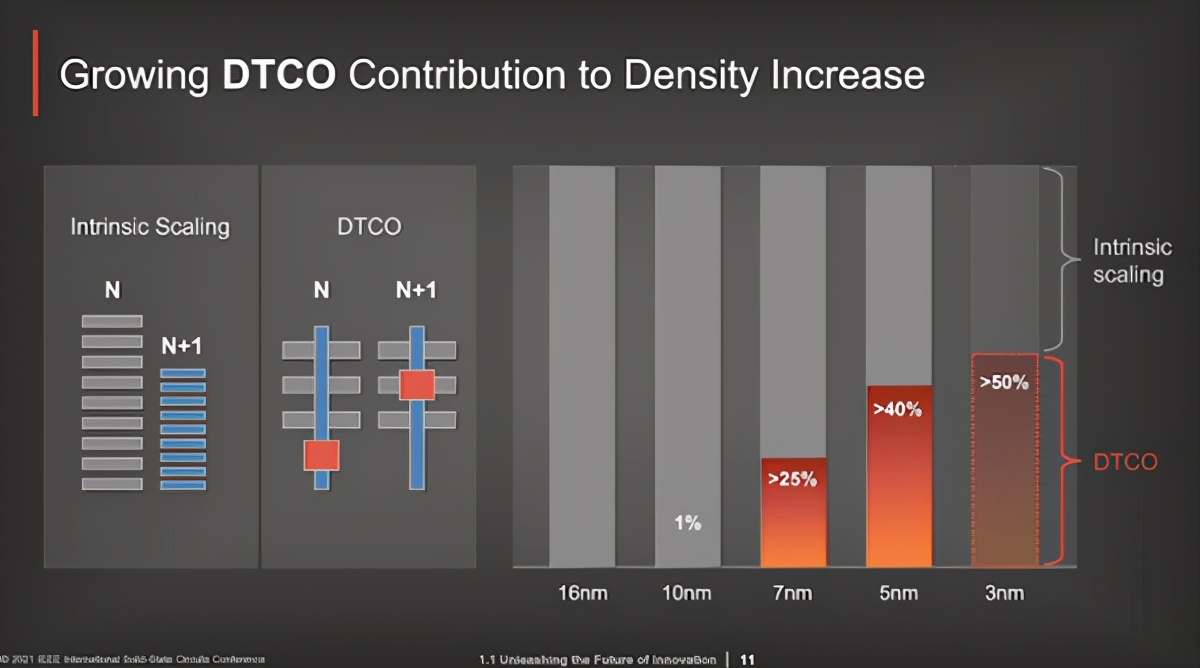

得益于极紫外光刻(EUV)技术,台积电能够实现更高的保真度、缩短周期、并降低工艺的复杂性和缺陷率。

值得一提的是,台积电在 5nm 节点的十层掩模工艺中使用了 EUV 技术(具体包括线切割、接触、金属线图案),并用单层 EUV 取代了早期的多层深紫外(DUV)工艺。

奇谱科技

奇谱科技